| Part Number(s) (NSID) |

Top View | Type | Pins | MSL Rating | Peak Reflow | RoHS Status |

CAD Symbols | Models | Package Marking Format |

|---|---|---|---|---|---|---|---|---|---|

| ADC08B3000CIYB/NOPB ADC08B3000CIYB |

LQFP EXP PAD | 128 | 3 3 |

260 260 |

Detail | Download | N/A |

NSUZXYYTTE# ADC08B3000 CIYB |

Description

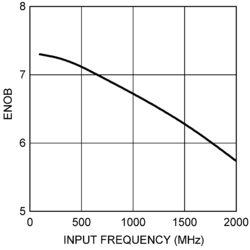

The ADC08B3000 is a single, low power, high performance CMOS analog-to-digital converter that digitizes signals to 8 bits resolution at sample rates up to 3.4 Gigasamples Per Second, (Gsps). Consuming a typical 1.6 Watts at 3 Gsps from a single 1.9 Volt supply, this device is guaranteed to have no missing codes over the full operating temperature range. The unique folding and interpolating architecture, the fully differential comparator design, the innovative design of the internal sample-and-hold amplifier and the calibration scheme enable an excellent response of all dynamic parameters up to Nyquist, producing a high 7.1 Effective Number Of Bits, (ENOB), with a 748 MHz input signal and a 3 GHz sample rate while providing a 10

The converter typically consumes less than 25 mW in the Power Down Mode and is available in a 128-lead, thermally enhanced exposed pad LQFP and operates over the Industrial (-40<C

|

Resolution |

8 Bits |

|

Max Conversion Rate |

3 Gsps (min) |

|

Code Error Rate |

10 |

|

ENOB @ 748 MHz Input |

7.1 Bits (typ) |

|

SNR @ 748 MHz |

44.9 dB (typ) |

|

Full Power Bandwidth |

3 GHz (typ) |

Power Consumption

|

Full Power Capture |

1.6 W (typ) |

|

Power Down Mode |

25 mW (typ) |

| • | Distance Ranging |

| • | Test and Measurement |

| • | Single +1.9V \0.1V Operation |

| • | Choice of SDR or DDR output clocking |

| • | Internal selectable 4K Data Buffer |

| • | Serial Interface for Extended Control |

| • | Adjustment of Input Full-Scale Range, Offset and Clock Phase |

| • | Duty Cycle Corrected Sample Clock |

| • | Test Pattern Output Capability |

Diagrams

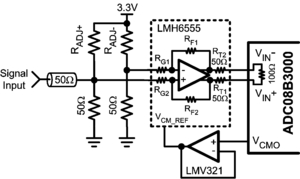

Typical Application

DC Coupled Analog Input

|

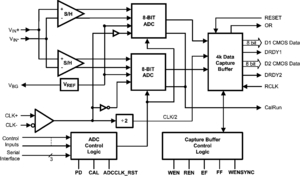

Block Diagram

|

Typical Performance  ENOB vs. INPUT FREQUENCY

|