# Power Management & Drives

| Revision H | listory: 2010-09-20                | Version 1.2 |  |  |  |  |  |

|------------|------------------------------------|-------------|--|--|--|--|--|

| Previous V | Previous Version: 1.1              |             |  |  |  |  |  |

| Page       | Subjects (major changes since 1.1) |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

|            |                                    |             |  |  |  |  |  |

Edition 2010-09-20

2ED020I12FA

Published by Infineon Technologies AG, Campeon 1-12, 85579 Neubiberg, Germany © Infineon Technologies AG 2010. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics. Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### **Information**

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# **EICEDRIVER®**

# **2ED020I12FA**

# **Dual IGBT Driver IC**

# **Product Highlights**

- · Coreless transformer isolated driver

- Galvanic Insulation

- Integrated protection features

- Suitable for operation at high ambient temperature

- Automotive Qualified (pending)

#### **Features**

- · Dual channel isolated IGBT Driver

- For 600V/1200V IGBTs

- 2A rail-to-rail output

- Vcesat-detection

- Active Miller Clamp

# Typical Application

- AC and Brushless DC Motor Drives

- High Voltage DC/DC-Converter

- UPS-Systems

- Welding

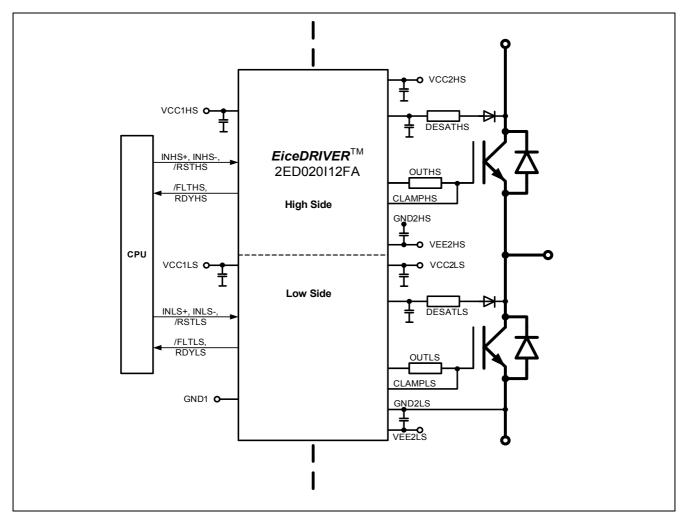

Figure 1: Typical Application

| 2ED020I12FA | Type        | Gate drive current | Package        |

|-------------|-------------|--------------------|----------------|

| 7 2.1       | 2ED020I12FA | +/- 2A             | PG-DSO-36/32-1 |

Preliminary Datasheet 3 Version 1.2, 2010-09-20

| 1     | Block Diagram and Application                                               | 7  |

|-------|-----------------------------------------------------------------------------|----|

| 2     | Functional Description                                                      | 9  |

| 2.1   | Introduction                                                                | 9  |

| 2.2   | Internal Protection Features                                                | 9  |

| 2.2.1 | Undervoltage Lockout (UVLO)                                                 | 9  |

| 2.2.2 | READY status output                                                         | 10 |

| 2.2.3 | Watchdog Timer                                                              | 10 |

| 2.2.4 | Active Shut-Down                                                            | 10 |

| 2.3   | Non-Inverting and Inverting Inputs                                          | 10 |

| 2.4   | Driver Outputs                                                              | 10 |

| 2.5   | External Protection Features                                                | 10 |

| 2.5.1 | Desaturation Protection                                                     | 10 |

| 2.5.2 | Short Circuit Clamping                                                      |    |

| 2.6   | RESET                                                                       | 11 |

| 3     | Pin Configuration and Functionality                                         | 12 |

| 3.1   | Pin Configuration                                                           |    |

| 3.2   | Pin Functionality                                                           |    |

| 4     | Electrical Parameters                                                       | 16 |

| 4.1   | Absolute Maximum Ratings                                                    |    |

| 4.2   | Operating Parameters                                                        |    |

| 4.3   | Recommended Operating Parameters                                            |    |

| 4.4   | Electrical Characteristics                                                  |    |

| 4.4.1 | Voltage Supply                                                              | 19 |

| 4.4.2 | Logic Input and Output                                                      | 19 |

| 4.4.3 | Gate Driver                                                                 | 21 |

| 4.4.4 | Short Circuit Clamping                                                      | 21 |

| 4.4.5 | Dynamic Characteristics                                                     |    |

| 4.4.6 | Desaturation protection                                                     | 23 |

| 4.4.7 | Active Shut Down                                                            | 23 |

| 5     | Insulation Characteristics                                                  | 24 |

| 5.1   | Complies with DIN EN 60747-5-2 (VDE 0884 Teil 2): 2003-01. Basic Insulation |    |

| 5.2   | Complies with UL 1577                                                       | 24 |

| 5.3   | Reliability                                                                 | 24 |

| 6     | Timing Diagramms                                                            | 25 |

| 7     | Package Outlines                                                            | 26 |

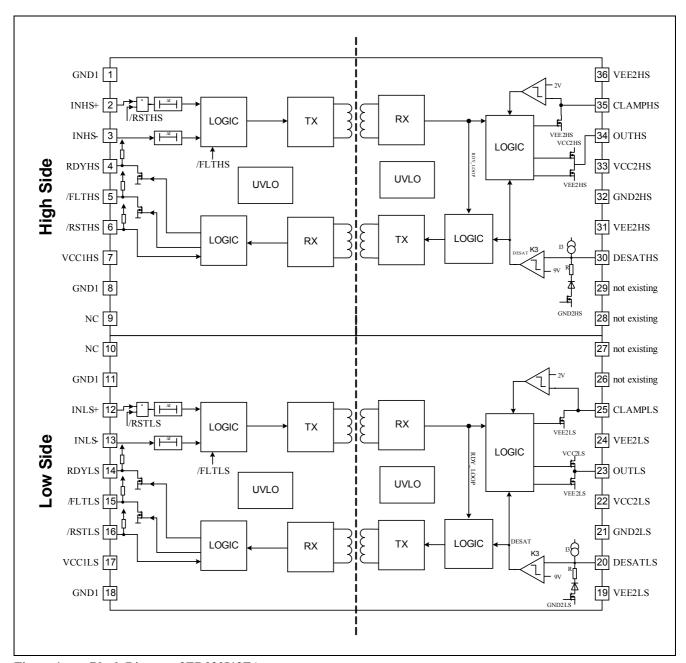

**Block Diagram and Application**

# 1 Block Diagram and Application

Figure 1: Block Diagram 2ED020I12FA

**Block Diagram and Application**

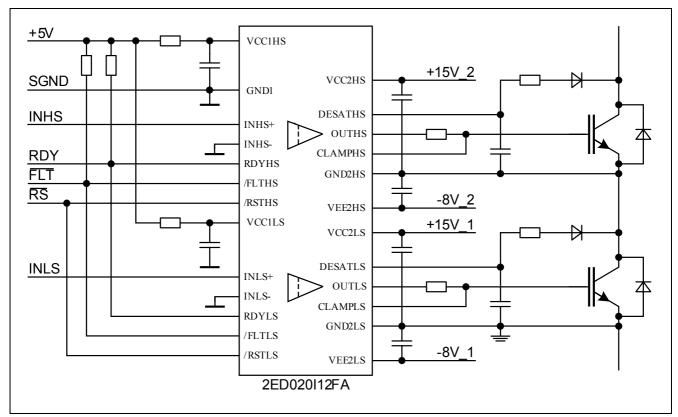

Figure 2: Application Example

**Functional Description**

# **2** Functional Description

#### 2.1 Introduction

The 2ED020I12FA is an advanced IGBT dual gate driver that can be also used for driving power MOS devices. Control and protection functions are included to make possible the design of high reliability systems.

The device consists of two galvanic separated driver. The input can be directly connected to a standard 5V DSP or microcontroller with CMOS in/output and the output driver are connected to the high side and low side switch.

The rail-to-rail driver outputs enables the user to provide easy clamping of the IGBTs gate voltage during short circuit of the IGBT. So an increase of short circuit current due to the feedback via the Miller capacitance can be avoided. Further, a rail-to-rail output reduces power dissipation.

The device also includes IGBT desaturation protection with FAULT status outputs.

Two READY status outputs reports if the device is supplied and operates correctly.

#### 2.2 Internal Protection Features

#### 2.2.1 Undervoltage Lockout (UVLO)

To ensure correct switching of IGBTs the device is equipped with undervoltage lockout for all driver outputs as well as for input section.

If the power supply voltage  $V_{VCC1xx}$  of the input section drops below  $V_{UVLOL1}$  a turn-off signal is sent to the output driver before power-down. The IGBT is switched off and the signals at INxx+ and INxx- are ignored as long as  $V_{VCC1xx}$  reaches the power-up voltage  $V_{UVLOH1}$ .

If the power supply voltage  $V_{VCC2xx}$  of the output driver goes down below  $V_{UVLOL2}$  the IGBT is switched off and signals from the input chip are ignored as long as  $V_{VCC2xx}$  reaches the power-up voltage  $V_{UVLOH2}$ . VEE2 is not monitored, otherwise negative supply voltage range from 0V to -12V would not be possible.

Preliminary Datasheet 9 Version 1.2, 2010-09-20

**Functional Description**

### 2.2.2 READY status output

The READY outputs shows the status of three internal protection features.

- UVLO of the input chip

- UVLO of the output chip after a short delay

- Internal signal transmission

It is not necessary to reset the READY signal since its state only depends on the status of the former protection signals.

### 2.2.3 Watchdog Timer

During normal operation the internal signal transmission is monitored by a watchdog timer. If the transmission fails for a given time, the IGBT is switched off and the READY output reports an internal error.

#### 2.2.4 Active Shut-Down

The Active Shut-Down feature ensures a safe IGBT off-state if the output chip is not connected to the power supply.

#### 2.3 Non-Inverting and Inverting Inputs

There are two possible input modes to control the IGBT. At non-inverting mode INxx+ controls the driver output while INxx- is set to low. At inverting mode INxx- controls the driver output while INxx+ is set to high. A minimum input pulse width is defined to filter occasional glitches.

#### 2.4 Driver Outputs

The output driver sections uses only MOSFETs to provide a rail-to-rail output. This feature permits that tight control of gate voltage during on-state and short circuit can be maintained as long as the drivers supply is stable. Due to the low internal voltage drop, switching behaviour of the IGBT is predominantly governed by the gate resistor. Furthermore, it reduces the power to be dissipated by the driver.

#### 2.5 External Protection Features

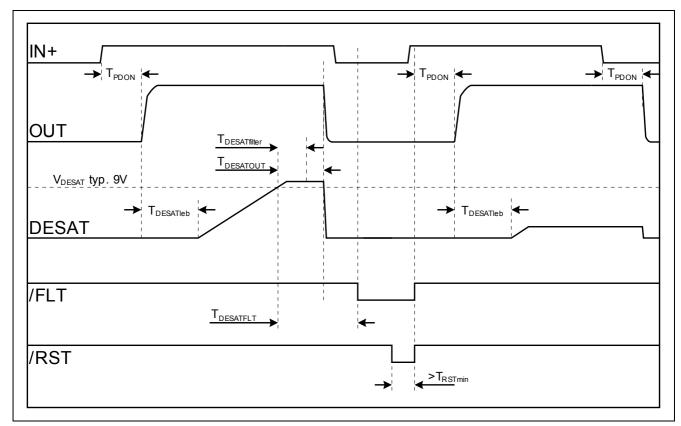

#### 2.5.1 Desaturation Protection

A desaturation protection ensures the protection of the IGBT at short circuit. When the DESAT voltage goes up and reaches 9V, the output is driven low. Further, the FAULT output is activated. A programmable blanking time is used to allow enough time for IGBT saturation. Blanking time is provided by a highly precise internal current source and an external capacitor.

# 2.5.2 Short Circuit Clamping

During short circuit the IGBTs gate voltage tends to rise because of the feedback via the Miller capacitance. An additional protection circuit connected to OUTxx limits this voltage to a value slightly higher than the supply voltage. A current of maximum 500 mA for 10us may be fed back to the supply through one of this paths. If higher currents are expected or a tighter clamping is desired external Schottky diodes may be added.

#### 2.6 RESET

The reset inputs have two functions.

Preliminary Datasheet 10 Version 1.2, 2010-09-20

#### **Functional Description**

Firstly, /RSTxx is in charge of setting back the FAULT output. If /RSTxx is low longer than a given time , /FLTxx will be reseted at the rising edge of /RSTxx; otherwise, it will remain unchanged. Moreover, it works as enable/shutdown of the input logic.

Preliminary Datasheet 11 Version 1.2, 2010-09-20

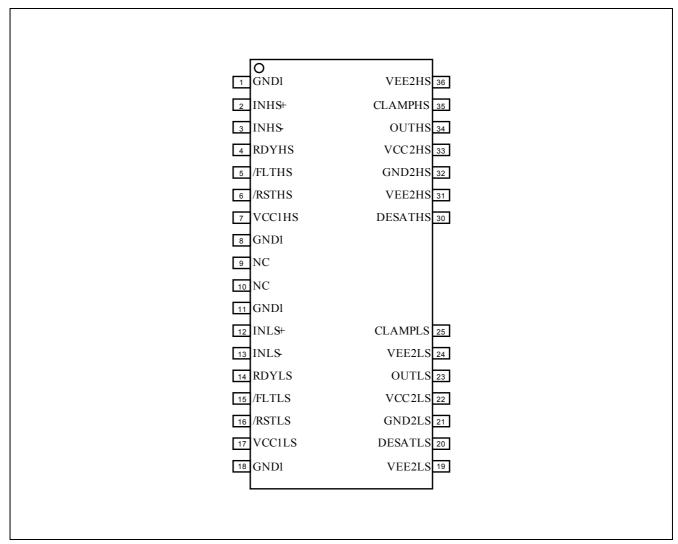

# 3 Pin Configuration and Functionality

# 3.1 Pin Configuration

| Pin | Symbol  | Function                                 |

|-----|---------|------------------------------------------|

| 1   | GND1    | Signal ground input side                 |

| 2   | INHS+   | Non inverted driver input high side      |

| 3   | INHS-   | Inverted driver input high side          |

| 4   | RDYHS   | Ready output high side                   |

| 5   | /FLTHS  | Inverted fault output high side          |

| 6   | /RSTHS  | Inverted reset input high side           |

| 7   | VCC1HS  | Positive power supply input high side    |

| 8   | GND1    | Signal ground input side                 |

| 9   | NC      | Not used, internally connected to Pin 10 |

| 10  | NC      | Not used, internally connected to Pin 9  |

| 11  | GND1    | Signal ground input side                 |

| 12  | INLS+   | Non inverted driver input low side       |

| 13  | INLS-   | Inverted driver input lowside            |

| 14  | RDYLS   | Ready output low side                    |

| 15  | /FLTLS  | Inverted fault output low side           |

| 16  | /RSTLS  | Inverted reset input low side            |

| 17  | VCC1LS  | Positive power supply input low side     |

| 18  | GND1LS  | Signal ground input side                 |

| 19  | VEE2LS  | Negative power supply low side driver    |

| 20  | DESATLS | Desaturation protection low side driver  |

| 21  | GND2LS  | Signal ground low side driver            |

| 22  | VCC2LS  | Power supply low side driver             |

| 23  | OUTLS   | Output low side driver                   |

| 24  | VEE2LS  | Negative power supply low side driver    |

| 25  | CLAMPLS | Miller clamping low side driver          |

| 26  |         | Pin not existing, cut out                |

| 27  |         | Pin not existing, cut out                |

| 28  |         | Pin not existing, cut out                |

| 29  |         | Pin not existing, cut out                |

| 30  | DESATHS | Desaturation protection high side driver |

| 31  | VEE2HS  | Negative power supply high side driver   |

| 32  | GND2HS  | Signal ground high side driver           |

| 33  | VCC2HS  | Power supply high side driver            |

| 34  | OUTHS   | Output high side driver                  |

| 35  | CLAMPHS | Miller clamping high side driver         |

| 36  | VEE2HS  | Negative power supply high side driver   |

Figure 3: PG-DSO 36/32-1/32-1 (top view)

### 3.2 Pin Functionality

#### GND1

Common ground connection of the input side.

#### **INHS+ Non-inverting driver input (High side)**

INHS+ control signal for the driver output if INHS- is set to low. (The IGBT is on if INHS+ = high and INHS- = low)

A minimum pulse width is defined to make the IC robust against glitches at IN+. An internal Pull-Down-Resistor ensures IGBT Off-State.

#### **INHS- Inverting driver input (High side)**

INHS- control signal for driver output if INHS+ is set to high. (IGBT is on if INHS- = low and INHS+ = high)

A minimum pulse width is defined to make the IC robust against glitches at INHS-. An internal Pull-Up-Resistor ensures IGBT Off-State.

#### /RSTHS (Reset input High side)

<u>Function 1:</u> Enable/shutdown of the input chip. (The IGBT is off if /RSTHS = low). A minimum pulse width is defined to make the IC robust against glitches at INHS-.

<u>Function 2:</u> Resets the DESAT-FAULT-state of the chip if /RSTHS is low for a time  $T_{RST}$ . An internal Pull-Up-Resistor is used to ensure /FLTHS status output.

#### /FLTHS (Fault output High side)

Open-drain output to report a desaturation error of the IGBT (/FLTHS is low if desaturation occurs)

#### **RDYHS** (Ready status High side)

Open-drain output to report the correct operation of the device. (RDYHS = high if both chips are above the UVLO level and the internal chip transmission is faultless)

#### VCC1HS (High side)

5V power supply of the input chip

#### **VEE2HS (High side)**

Negative power supply pins of the output chip. If no negative supply voltage is available, both pins have to be connected to GND2HS.

#### **DESATHS (Desaturation High side)**

Monitoring of the IGBT saturation voltage ( $V_{CE}$ ) to detect desaturation caused by short circuits. If OUT is high,  $V_{CE}$  is above a defined value and a certain blanking time has expired, the desaturation protection is activated and the IGBT is switched off. The blanking time is adjustable by an external capacitor.

#### **CLAMPHS (Clamping)**

Ties the gate voltage to ground after the IGBT has been switched off at a defined voltage to avoid a parasitic switch-on of the IGBT.During turn-off, the gate voltage is monitored and the clamp output is activated when the gate voltage goes below 2V (related to VEE2HS).

#### **GND2HS** (High side)

Reference ground of the output chip.

#### **OUTHS (Driver output High side)**

Output pin to drive an IGBT. The voltage is switched between VEE2HS and VCC2HS. In normal operating mode Vout is controlled by INHS+, INHS- and /RSTHS. During error mode (UVLO, internal error or DESATHS Vout is set to VEE2HS independent of the input control signals.

#### VCC2HS (High side)

Positive power supply pin of the output side.

#### **GND1LS (Low side)**

Ground connection of the input side.

### INLS+ Non-inverting driver input (Low side)

INLS+ control signal for the driver output if INLS- is set to low. (The IGBT is on if INLS+ = high and INLS- = low)

A minimum pulse width is defined to make the IC robust against glitches at IN+. An internal Pull-Down-Resistor ensures IGBT Off-State.

#### **INLS- Inverting driver input (Low side)**

INLS- control signal for driver output if INLS+ is set to high. (IGBT is on if INLS- = low and INLS+ = high)

A minimum pulse width is defined to make the IC robust against glitches at INLS-. An internal Pull-Up-Resistor ensures IGBT Off-State.

#### /RSTLS (Reset input Low side)

<u>Function 1:</u> Enable/shutdown of the input chip. (The IGBT is off if /RSTLS = low). A minimum pulse width is defined to make the IC robust against glitches at INLS-.

<u>Function 2:</u> Resets the DESAT-FAULT-state of the chip if /RSTLS is low for a time  $T_{RST}$ . An internal Pull-Up-Resistor is used to ensure /FLTLS status output.

#### /FLTLS (Fault output Low side)

Open-drain output to report a desaturation error of the IGBT (/FLTLS is low if desaturation occurs)

#### **RDYLS (Ready status Low side)**

Open-drain output to report the correct operation of the device. (RDYLS = high if both chips are above the UVLO level and the internal chip transmission is faultless)

#### VCC1LS (Low side)

5V power supply of the input chip

#### VEE2LS (Low side)

Negative power supply pins of the output chip. If no negative supply voltage is available, both pins have to be connected to GND2LS.

#### **DESATLS** (Desaturation Low side)

Monitoring of the IGBT saturation voltage ( $V_{CE}$ ) to detect desaturation caused by short circuits. If OUT is high,  $V_{CE}$  is above a defined value and a certain blanking time has expired, the desaturation protection is activated and the IGBT is switched off. The blanking time is adjustable by an external capacitor.

#### **CLAMPLS (Clamping)**

Ties the gate voltage to ground after the IGBT has been switched off at a defined voltage to avoid a parasitic switch-on of the IGBT.During turn-off, the gate voltage is monitored and the clamp output is activated when the gate voltage goes below 2V (related to VEE2LS).

#### **GND2LS (Low side)**

Reference ground of the output chip.

#### **OUTLS (Driver output Low side)**

Output pin to drive an IGBT. The voltage is switched between VEE2LS and VCC2LS. In normal operating mode Vout is controlled by INLS+, INLS- and /RSTLS. During error mode (UVLO, internal error or DESATLS Vout is set to VEE2LS independent of the input control signals.

#### VCC2LS (Low side)

Positive power supply pin of the output side.

Preliminary Datasheet 15 Version 1.2, 2010-09-20

# **4** Electrical Parameters

### 4.1 Absolute Maximum Ratings

Note: Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction of the integrated circuit. Unless otherwise noted all parameters refer to GND1. The specification for all driver signals is valid for HS and LS with out special notic, e.g. IN+ covers INHS+ as well as INLS+. The signals from driver output side are measured with respect to their specific GND2HS or GND2LS.

| Parameter                                                                        | Symbol               | Symbol Limit Values    |                        | Unit | Remarks                                                                                 |  |

|----------------------------------------------------------------------------------|----------------------|------------------------|------------------------|------|-----------------------------------------------------------------------------------------|--|

|                                                                                  |                      | min.                   | max.                   |      |                                                                                         |  |

| Positive power supply output side                                                | V <sub>VCC2</sub>    | -0.3                   | 20                     | V    | 1)                                                                                      |  |

| Negative power supply output side                                                | $V_{ m VEE2}$        | -12                    | 0.3                    | V    | 1)                                                                                      |  |

| Maximum power supply voltage output side (V <sub>VCC2</sub> -V <sub>VEE2</sub> ) | V <sub>max2</sub>    |                        | 28                     | V    |                                                                                         |  |

| Gate driver output                                                               | V <sub>OUT</sub>     | V <sub>VEE2</sub> -0.3 | V <sub>max2</sub> +0.3 | V    |                                                                                         |  |

| Gate driver high output maximum current                                          | $I_{OUT}$            |                        | 2.4                    | A    | $t = 2\mu s$                                                                            |  |

| Gate driver low output maximum current                                           | $I_{OUT}$            |                        | 2.4                    | A    | $t = 2\mu s$                                                                            |  |

| Maximum short circuit clamping time                                              | $t_{CLP}$            |                        | 10                     | us   | $I_{\text{CLAMP/OUT}} = 500 \text{mA}$                                                  |  |

| Positive power supply input side                                                 | V <sub>VCC1</sub>    | -0.3                   | 6.5                    | V    |                                                                                         |  |

| Logic input voltages<br>(IN+,IN-,\overline{RST})                                 | V <sub>LogicIN</sub> | -0.3                   | 6.5                    | V    |                                                                                         |  |

| Opendrain Logic output voltage<br>(FLT)                                          | $V_{\overline{FLT}}$ | -0.3                   | 6.5                    | V    |                                                                                         |  |

| Opendrain Logic output voltage<br>(RDY)                                          | $V_{RDY}$            | -0.3                   | 6.5                    | V    |                                                                                         |  |

| Opendrain Logic output current (FAULT)                                           | $I_{\overline{FLT}}$ |                        | 10                     | mA   |                                                                                         |  |

| Opendrain Logic output current (RDY)                                             | $I_{RDY}$            |                        | 10                     | mA   |                                                                                         |  |

| Pin DESAT voltage                                                                | $V_{ m DESAT}$       | -0.3                   | V <sub>VCC2</sub> +0.3 |      | $^{1)}V_{VEE2} = -8V$                                                                   |  |

| Junction temperature                                                             | $T_{\mathrm{J}}$     | -40                    | 150                    | °C   |                                                                                         |  |

| Storage temperature                                                              | $T_S$                | -55                    | 150                    | °C   |                                                                                         |  |

| Power dissipation, per input part                                                | P <sub>D, IN</sub>   |                        | 100                    | mW   | $^{2)}$ @TA = 25°                                                                       |  |

| Power dissipation, per output part                                               | P <sub>D, OUT</sub>  |                        | 400                    | mW   | $^{2)}$ @TA = 25°                                                                       |  |

| Power dissipation, total                                                         | P <sub>D, tot</sub>  |                        | 1000                   | mW   | $^{2)}$ @TA = 25°                                                                       |  |

| Thermal resistance (Input part)                                                  | R <sub>THJA,IN</sub> | _                      | 375                    | K/W  | $^{2)}$ @TA = 25°C,<br>$P_{D, IN\_HS+LS} =$<br>200mW,<br>$P_{D, OUT\_HS+LS} =$<br>800mW |  |

| Thermal resistance (Output part) | R <sub>THJA,OUT</sub> |   | 110 | K/W | $^{2)}$ @TA = 25°C,<br>$P_{D, IN\_HS+LS} =$<br>200mW,<br>$P_{D, OUT\_HS+LS} =$<br>800mW |

|----------------------------------|-----------------------|---|-----|-----|-----------------------------------------------------------------------------------------|

| ESD Capability                   | $V_{ESD}$             | _ | tbd | kV  | Human Body<br>Model <sup>3)</sup>                                                       |

<sup>1)</sup> With respect to GND2.

Preliminary Datasheet 17 Version 1.2, 2010-09-20

<sup>2)</sup> IC power dissipation is derated linearly at 12mW/°C above 65°C. Thermal performance may change significantly with layout and heat dissipation of components in close proximity.

<sup>3)</sup> According to EIA/JESD22-A114-B (discharging a 100pF capacitor through a  $1.5k\Omega$  series resistor).

# 4.2 **Operating Parameters**

Note: Within the operating range the IC operates as described in the functional description. Unless otherwise noted all parameters refer to GND1. The specification for all driver signals is valid for HS and LS with out special notic, e.g. IN+ covers INHS+ as well as INLS+. The signals from driver output side are measured with respect to their specific GND2HS or GND2LS

| Parameter                                                                        | Symbol                          | Limit Values |            | Unit  | Remarks |  |

|----------------------------------------------------------------------------------|---------------------------------|--------------|------------|-------|---------|--|

|                                                                                  |                                 | min.         | max.       |       |         |  |

| Positive power supply output side                                                | $V_{VCC2}$                      | 13           | 20         | V     | 1)      |  |

| Negative power supply output side                                                | $ m V_{ m VEE2}$                | -12          | 0          | V     | 1)      |  |

| Maximum power supply voltage output side (V <sub>VCC2</sub> -V <sub>VEE2</sub> ) | V <sub>max2</sub>               |              | 28         | V     |         |  |

| Positive power supply input side                                                 | V <sub>VCC1</sub>               | 4.5          | 5.5        | V     |         |  |

| Logic input voltages (IN+,IN-,RST)                                               | $V_{LogicIN}$                   | -0.3         | 5.5        | V     |         |  |

| Pin DESAT voltage                                                                | $V_{ m DESAT}$                  | -0.3         | $V_{VCC2}$ | V     | 1)      |  |

| Ambient temperature                                                              | $T_A$                           | -40          | 125        | °C    |         |  |

| Common mode transient immunity <sup>2)</sup>                                     | $ \Delta V_{\rm ISO}/{\rm d}t $ | _            | 50         | kV/μs | @ 500V  |  |

<sup>1)</sup> With respect to GND2.

#### 4.3 Recommended Operating Parameters

Note: Unless otherwise noted all parameters refer to GND1. The specification for all driver signals is valid for HS and LS with out special notic, e.g. IN+ covers INHS+ as well as INLS+. The signals from driver output side are measured with respect to their specific GND2HS or GND2LS

| Parameter                         | Symbol            | Values | Unit | Remarks |

|-----------------------------------|-------------------|--------|------|---------|

|                                   |                   |        |      |         |

| Positive power supply output side | $V_{VCC2}$        | 15     | V    | 1)      |

| Negative power supply output side | $ m V_{ m VEE2}$  | -8     | V    | 1)      |

| Positive power supply input side  | V <sub>VCC1</sub> | 5      | V    |         |

<sup>1)</sup> With respect to GND2.

<sup>2)</sup> The parameter is not subject to production test - verified by design/characterization

#### 4.4 Electrical Characteristics

Note: The electrical characteristics involve the spread of values for the supply voltages, load and junction temperatures given below. Typical values represent the median values, which are related to production processes at  $T=25\,^{\circ}\text{C}$ . Unless otherwise noted all voltages are given with respect to GND. The specification for all driver signals is valid for HS and LS with out special notic, e.g. IN+ covers INHS+ as well as INLS+. The signals from driver output side are measured with respect to their specific GND2HS or GND2LS

# 4.4.1 Voltage Supply.

| Parameter                                                                | Symbol            | Limit Va | Limit Values |      |    | <b>Test Conditions</b>                                                                                  |

|--------------------------------------------------------------------------|-------------------|----------|--------------|------|----|---------------------------------------------------------------------------------------------------------|

|                                                                          |                   | min.     | typ.         | max. |    |                                                                                                         |

| UVLO Threshold Input Chip                                                | $V_{UVLOH1}$      | _        | 4.1          | 4.3  | V  |                                                                                                         |

|                                                                          | $V_{UVLOL1}$      | 3.5      | 3.8          |      | V  |                                                                                                         |

| UVLO Hysteresis Input Chip                                               | $V_{\rm HYS1}$    | 0.15     | _            |      | V  |                                                                                                         |

| $(V_{UVLOH1} - V_{UVLOL1})$                                              |                   |          |              |      |    |                                                                                                         |

| UVLO Threshold Output Chip                                               | $V_{UVLOH2}$      | _        | 12.0         | 12.6 | V  |                                                                                                         |

|                                                                          | $V_{\rm UVLOL2}$  | 10.4     | 11.0         |      | V  |                                                                                                         |

| UVLO Hysteresis Output Chip (V <sub>UVLOH1</sub> - V <sub>UVLOL1</sub> ) | V <sub>HYS2</sub> | 0.7      | 0.9          |      | V  |                                                                                                         |

| Quiescent Current Input Chip                                             | $I_{Q1}$          | _        | 7            | 9    | mA | V <sub>VCC1</sub> =5V<br>IN+ = High, IN- = Low<br>=>OUT = High, RDY =<br>High, /FLT = High              |

| Quiescent Current Output Chip                                            | $I_{Q2}$          | _        | 4            | 6    | mA | $V_{VCC2}$ =15V<br>$V_{VEE2}$ =-8V<br>IN+ = High, IN- = Low<br>=>OUT = High, RDY =<br>High, /FLT = High |

# 4.4.2 Logic Input and Output

| Parameter                                       | Symbol                                                                                         | Limit Values |      |      | Unit | <b>Test Conditions</b>                        |

|-------------------------------------------------|------------------------------------------------------------------------------------------------|--------------|------|------|------|-----------------------------------------------|

|                                                 |                                                                                                | min.         | typ. | max. |      |                                               |

| IN+,IN-, RST Low Input Voltage                  | $\begin{matrix} V_{\text{IN+L},} V_{\text{IN-}} \\ L, V_{\overline{\text{RSTL}}} \end{matrix}$ |              |      | 1.5  | V    |                                               |

| IN+,IN-, RST High Input Voltage                 | $V_{\text{IN+H,}}V_{\text{IN-}}$ $_{\text{H}}V_{\overline{\text{RSTH}}}$                       | 3.5          |      | _    | V    |                                               |

| IN-, RST Input Current                          | $I_{\text{IN-,}}I_{\overline{\text{RST}}}$                                                     |              | 100  | 400  | uA   | $V_{IN}$ =GND1<br>$V_{\overline{RST}}$ =GND1  |

| IN+ Input Current                               | I <sub>IN+,</sub>                                                                              | _            | 100  | 400  | uA   | V <sub>IN+</sub> =VCC1                        |

| RDY,FLT Pull Up Current                         | $\begin{matrix} I_{PRDY,} \\ I_{\overline{PFLT}} \end{matrix}$                                 |              | 100  | 400  | uA   | $V_{RDY}$ =GND1<br>$V_{\overline{FLT}}$ =GND1 |

| Input Pulse Suppression IN+, IN-                | $T_{MININ+},$ $T_{MININ-}$                                                                     | 30           | 40   | _    | ns   |                                               |

| Input Pulse Suppression RST for ENABLE/SHUTDOWN | T <sub>MINRST</sub>                                                                            | 30           | 40   |      | ns   |                                               |

| Pulse Width RST for Reseting FLT                | T <sub>RST</sub>                                                                               | 800          |      |      | ns   |                                               |

| FLT Low Voltage | $V_{FLTL}$ | <br> | 300 | mV | $I_{SINK(\overline{FLT})} = 5mA$ |

|-----------------|------------|------|-----|----|----------------------------------|

| RDY Low Voltage | $V_{RDYL}$ | <br> | 300 | mV | $I_{SINK(RDY)} = 5mA$            |

# 4.4.3 Gate Driver

| Parameter                      | Symbol             | l Limit Values        |                         |                         |   | t Test Conditions                                                                    |  |

|--------------------------------|--------------------|-----------------------|-------------------------|-------------------------|---|--------------------------------------------------------------------------------------|--|

|                                |                    | min.                  | typ.                    | max.                    |   |                                                                                      |  |

| High Level Output Voltage      | V <sub>OUTH1</sub> | V <sub>CC2</sub> -1.2 | V <sub>CC2</sub> -0.8   |                         | V | $I_{OUTH} = -20 \text{mA}$                                                           |  |

|                                | V <sub>OUTH2</sub> | V <sub>CC2</sub> -2.5 | V <sub>CC2</sub> -2     |                         | V | $I_{OUTH} = -200 \text{mA}$                                                          |  |

|                                | V <sub>OUTH3</sub> | V <sub>CC2</sub> -9   | V <sub>CC2</sub> -5     |                         | V | $I_{OUTH} = -1A$                                                                     |  |

|                                | V <sub>OUTH4</sub> |                       | V <sub>CC2</sub> -10    |                         | V | $I_{OUTH} = -2A$                                                                     |  |

| High Level Output Peak Current | I <sub>OUTH</sub>  | -1.5                  | -2                      | _                       | A | IN+=High, IN-=Low;<br>OUT = High                                                     |  |

| Low Level Output Voltage       | V <sub>OUTL1</sub> |                       | V <sub>VEE2</sub> +0.04 | V <sub>VEE2</sub> +0.09 | V | $I_{OUTL} = 20 \text{mA}$                                                            |  |

|                                | V <sub>OUTL2</sub> |                       | V <sub>VEE2</sub> +0.3  | V <sub>VEE2</sub> +0.85 | V | $I_{OUTL} = 200 \text{mA}$                                                           |  |

|                                | V <sub>OUTL3</sub> | _                     | V <sub>VEE2</sub> +2.1  | V <sub>VEE2</sub> +5.0  | V | $I_{OUTL} = 1A$                                                                      |  |

|                                | V <sub>OUTL4</sub> |                       | V <sub>VEE2</sub> +7    |                         | V | $I_{OUTL} = 2A$                                                                      |  |

| Low Level Output Peak Current  | $I_{OUTL}$         | 1,5                   | 2                       | _                       | A | IN+=Low, IN-=Low;<br>OUT = Low,<br>V <sub>VCC2</sub> =15V,<br>V <sub>VEE2</sub> =-8V |  |

# 4.4.4 Short Circuit Clamping

| Parameter                                                     | Symbol              | Limit Values |      |      | Unit | <b>Test Conditions</b>                                                                               |

|---------------------------------------------------------------|---------------------|--------------|------|------|------|------------------------------------------------------------------------------------------------------|

|                                                               |                     | min.         | typ. | max. |      |                                                                                                      |

| Clamping voltage (OUT) (V <sub>OUT</sub> -V <sub>VCC2</sub> ) | V <sub>CLPout</sub> | _            | 0.8  | 1.3  | V    | IN+=High, IN-=Low,<br>OUT=High<br>I <sub>OUT</sub> = 500mA (pulse<br>test,t <sub>CLPmax</sub> =10us) |

# 4.4.5 **Dynamic Characteristics**

| Parameter                                                                                  | Symbol               | Limit Values |      |      | Unit | <b>Test Conditions</b>                                                    |

|--------------------------------------------------------------------------------------------|----------------------|--------------|------|------|------|---------------------------------------------------------------------------|

|                                                                                            |                      | min.         | typ. | max. |      |                                                                           |

| Input IN+ to output propagation delay ON                                                   | T <sub>PDON</sub>    | 150          | 170  | 190  | ns   | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V                             |

| Input IN+ to output propagation delay OFF                                                  | T <sub>PDOFF</sub>   | 145          | 165  | 185  | ns   | C <sub>LOAD</sub> = 100pF<br>V <sub>IN+</sub> =50%, V <sub>OUT</sub> =50% |

| Input IN+ to output propagation delay distortion (T <sub>PDOFF</sub> - T <sub>PDON</sub> ) | T <sub>PDISTO</sub>  | -35          | -5   | 25   | ns   | @ 25°C                                                                    |

| Input IN+ to output propagation delay ON variation due to temp                             | T <sub>PDONt</sub>   | 160          | 190  | 220  | ns   | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V                             |

| Input IN+ to output propagation delay OFF variation due to temp                            | T <sub>PDOFFt</sub>  | 165          | 195  | 225  | ns   | C <sub>LOAD</sub> = 100pF<br>V <sub>IN+</sub> =50%, V <sub>OUT</sub> =50% |

| Input IN+ to output propagation delay distortion (T <sub>PDOFF</sub> - T <sub>PDON</sub> ) | T <sub>PDISTOt</sub> | -25          | 5    | 35   | ns   | @ 125°C                                                                   |

| Input IN+ to output propagation delay ON variation due to temp                             | T <sub>PDONt</sub> | 135  | 165 | 195 | ns | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V                                              |

|--------------------------------------------------------------------------------------------|--------------------|------|-----|-----|----|--------------------------------------------------------------------------------------------|

| Input IN+ to output propagation delay OFF variation due to temp                            | $T_{PDOFFt}$       | 120  | 150 | 180 | ns | $C_{LOAD} = 100 pF$<br>$V_{IN+} = 50\%, V_{OUT} = 50\%$                                    |

| Input IN+ to output propagation delay distortion (T <sub>PDOFF</sub> - T <sub>PDON</sub> ) | $T_{PDISTOt}$      | -45  | -15 | 15  | ns | @ -40°C                                                                                    |

| Input IN- to output propagation delay ON                                                   | T <sub>PDON</sub>  | 135  | 155 | 750 | ns |                                                                                            |

| Input IN- to output propagation delay OFF                                                  | $T_{PDOFF}$        | 145  | 165 | 185 | ns | $V_{VCC2} = 15V, V_{VEE2} = -8V$ $C_{LOAD} = 100pF$ $V_{IN+} = 50\%, V_{OUT} = 50\%$       |

| Input IN- to output propagation delay distortion (T <sub>PDOFF</sub> - T <sub>PDON</sub> ) | $T_{PDISTO}$       | -565 | 10  | 40  | ns | @ 25°C                                                                                     |

| Input IN- to output propagation delay ON variation due to temp                             | T <sub>PDONt</sub> | 140  | 170 | 990 | ns | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V                                              |

| Input IN- to output propagation delay OFF variation due to temp                            | $T_{PDOFFt}$       | 165  | 195 | 225 | ns | $C_{LOAD} = 100 pF$<br>$V_{IN} = 50\%, V_{OUT} = 50\%$                                     |

| Input IN- to output propagation delay distortion (T <sub>PDOFF</sub> - T <sub>PDON</sub> ) | $T_{PDISTOt}$      | -770 | 25  | 55  | ns | @ 125°C                                                                                    |

| Input IN- to output propagation delay ON                                                   | $T_{PDON}$         | 120  | 150 | 990 | ns |                                                                                            |

| Input IN- to output propagation delay OFF                                                  | $T_{PDOFF}$        | 120  | 150 | 180 | ns | $V_{VCC2} = 15V, V_{VEE2} = -8V$ $C_{LOAD} = 100pF$ $V_{IN} = 50\%, V_{OUT} = 50\%$        |

| Input IN- to output propagation delay distortion (T <sub>PDOFF</sub> - T <sub>PDON</sub> ) | $T_{PDISTO}$       | -810 | 0   | 30  | ns | @ -40°C                                                                                    |

| Rise Time                                                                                  | T <sub>RISE</sub>  | 10   | 30  | 60  | ns | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V<br>C <sub>LOAD</sub> = 1nF<br>VL 10%,VH 90%  |

|                                                                                            |                    | 200  | 400 | 800 | ns | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V<br>C <sub>LOAD</sub> = 34nF<br>VL 10%,VH 90% |

| Fall Time                                                                                  | T <sub>FALL</sub>  | 10   | 50  | 90  | ns | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V<br>C <sub>LOAD</sub> = 1nF<br>VL 10%,VH 90%  |

|                                                                                            |                    | 200  | 350 | 600 | ns | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V<br>C <sub>LOAD</sub> = 34nF<br>VL 10%,VH 90% |

# 4.4.6 **Desaturation protection**

| rameter Symbol Limit Values          |                       |      |      | Unit | <b>Test Conditions</b> |                                                                                                |

|--------------------------------------|-----------------------|------|------|------|------------------------|------------------------------------------------------------------------------------------------|

|                                      |                       | min. | typ. | max. |                        |                                                                                                |

| Blanking Capacitor Charge Current    | I <sub>DESATC</sub>   | 450  | 500  | 550  | uA                     | $V_{\text{VCC2}} = 15\text{V}, V_{\text{VEE2}} = -8\text{V}$<br>$V_{\text{DESAT}} = 2\text{V}$ |

| Blanking Capacitor Discharge Current | I <sub>DESATD</sub>   | 10   | 13   |      | mA                     | $V_{\text{VCC2}}$ =15V, $V_{\text{VEE2}}$ =-8V<br>$V_{\text{DESAT}}$ =6V                       |

| Desaturation Reference Level         | V <sub>DESAT</sub>    | 8.3  | 9    | 9.5  | V                      | V <sub>VCC2</sub> =15V                                                                         |

| Desaturation Filter Time             | T <sub>DESATleb</sub> | -    | 250  | -    | ns                     | $V_{\text{VCC2}} = 15\text{V}, V_{\text{VEE2}} = -8\text{V}$<br>$V_{\text{DESAT}} = 9\text{V}$ |

| Desaturation Sense to OUT Low Delay  | T <sub>DESATOUT</sub> |      | 350  | 410  | ns                     | V <sub>OUT</sub> =90%<br>C <sub>LOAD</sub> = 1nF                                               |

| Desaturation Sense to FLT Low Delay  | $T_{DESATFLT}$        |      |      | 2.25 | us                     | $V_{\overline{FLT}}=10\%; I_{\overline{FLT}}=5mA$                                              |

| Desaturation Low Voltage             | V <sub>DESATL</sub>   | 0.4  | 0.6  | 0.95 | V                      | IN+=Low, IN-=Low,<br>OUT=Low                                                                   |

| Leading edge blanking                | T <sub>DESATleb</sub> | -    | 400  | -    | ns                     | not subject of production test                                                                 |

### 4.4.7 Active Shut Down

| Parameter                | Symbol                           | Limit Values |      |      | Unit | <b>Test Conditions</b>                             |

|--------------------------|----------------------------------|--------------|------|------|------|----------------------------------------------------|

|                          |                                  | min.         | typ. | max. | Ī    |                                                    |

| Active Shut Down Voltage | V <sub>ACTSD</sub> <sup>1)</sup> |              |      | 4    | V    | I <sub>OUT</sub> =-200mA,<br>V <sub>CC2</sub> open |

<sup>1)</sup> With reference to VEE2

**Insulation Characteristics**

# 5 Insulation Characteristics

# 5.1 Complies with DIN EN 60747-5-2 (VDE 0884 Teil 2): 2003-01. Basic Insulation

| Description                                                 | Symbol            | Characteristic | Unit       |

|-------------------------------------------------------------|-------------------|----------------|------------|

| Installation classification per EN 60664-1, Table 1         |                   |                |            |

| for rated mains voltage $\leq 150 \text{ V}_{\text{RMS}}$   |                   | I-IV           |            |

| for rated mains voltage $\leq 300 \text{ V}_{RMS}$          |                   | I-III          |            |

| for rated mains voltage $\leq 600 \text{ V}_{\text{RMS}}$   |                   | I-II           |            |

| Climatic Classification                                     |                   | 55/105/21      |            |

| Pollution Degree (EN 60664-1)                               |                   | 2              |            |

| Minimum External Clearance between input and driver section | CLR               | 8              | mm         |

| Minimum External Creepage between input and driver section  | CPG               | 8              | mm         |

| Minimum External Clearance between HS- and LS-driver output |                   | tbd            | mm         |

| Minimum External Creepage between HS- and LS-driver output  |                   | 2.81           | mm         |

| Minimum Comparative Tracking Index                          | CTI               | 175            |            |

| Maximum Repetitive Insulation Voltage                       | V <sub>IORM</sub> | 1420           | $V_{PEAK}$ |

| Highest Allowable Overvoltage                               | V <sub>IOTM</sub> | 6000           | $V_{PEAK}$ |

| Maximum Surge Insulation Voltage                            | V <sub>IOSM</sub> | 6000           | V          |

# 5.2 Complies with UL 1577

| Description                         | Symbol           | Characteristic | Unit             |

|-------------------------------------|------------------|----------------|------------------|

| Insulation Withstand Voltage / 1min | V <sub>ISO</sub> | 3750           | V <sub>rms</sub> |

| Insulation Test Voltage / 1sec      | $ m V_{ISO}$     | 4500           | V <sub>rms</sub> |

# 5.3 Reliability

For Qualification Report please contact your local Infineon Technologies office.

Preliminary Datasheet 24 Version 1.2, 2010-09-20

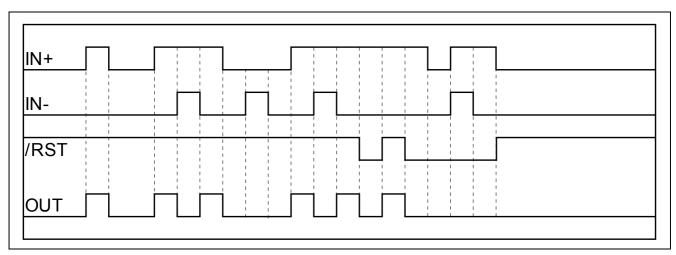

**Timing Diagramms**

# 6 Timing Diagramms

Figure 4: Typical Switching Behavior

Figure 5: DESAT Switch-Off Behavior

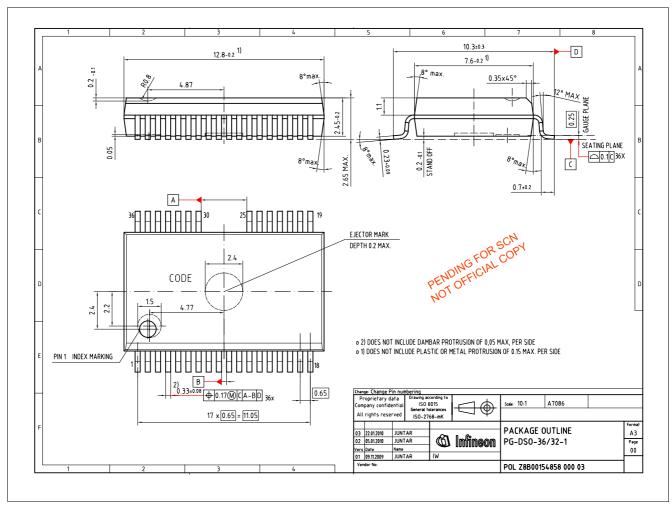

**Package Outlines**

# 7 Package Outlines

Figure 6: **PG-DSO 36/32-1**